记住用户名密码

金属互连中的纳米图案化固有选择性原子层沉积技术

2024年6月6日,《Chemistry of materials》在线发表了华科微纳中心陈蓉教授团队关于区域选择性沉积(ASD)技术在金属互连中利用固有选择性实现金属选择性沉积的文章Area selective deposition of Ru on W/SiO2 nanopatterns via sequential reactant dosing and thermal defect correction(通过多次短脉冲和热缺陷后处理在 W/SiO2 纳米图案上进行 Ru 的区域选择性沉积)”。博士生齐子廉为论文第一作者,陈蓉教授,曹坤副教授为论文通讯作者。

背景介绍

在半导体行业,我们不断努力开发更小、更高性能的纳米电子器件。实现这些器件的高分辨率图案化是确保其可制造性的关键。然而,由于纳米器件的尺寸缩小到原子尺度,堆叠误差成为高精度图案化的主要障碍。传统的“沉积-光刻-蚀刻”方法在控制边缘放置误差(EPE)和应对复杂步骤方面面临重大挑战。此外,采用新材料和3D纳米结构也对大批量制造(HVM)技术提出了更高要求。随着器件尺寸的进一步缩小和堆叠层数的增加,对高精度图案化薄膜的需求变得更加迫切。

原子层沉积(ALD)是一种重要的原子级薄膜制备方法。早在1998年,ALD技术便开始应用于非易失性存储器。到2007年,这项技术被用于英特尔公司45纳米芯片的高介电/金属栅极结构中。ALD技术通过前驱体和共反应物的交替暴露,利用分子单层吸附和反应,实现在表面逐层自限制性沉积,从而实现原子级厚度控制。ALD技术能够制备具有高深宽比和大面积均匀一致性的保形薄膜,是工业批量化制造的理想工具。

然而,传统的ALD技术通常会在整个表面均匀沉积,无法直接制备图案化薄膜。选择性原子层沉积(Selective ALD)利用表面特性的差异,在指定区域内沉积介电氧化物,具有堆叠精度高、工艺步骤简单的优势,是先进电子制造中的重要技术。选择性ALD使得以原子为基本构筑单元、自下而上地构建纳米结构的梦想变为现实,被认为是纳米制造领域的“终极解决方案”。

在以往的研究中,选择性沉积技术借助小分子抑制剂和单分子层钝化膜作为模板来阻挡特定区域的沉积。然而,当特征尺寸进一步缩小,对三维纳米结构的需求增加时,选择合适的分子模板变得更加困难。固有选择性ALD是一种不使用钝化分子层模板和去除步骤的方法,简化了工艺流程。固有选择性的主要挑战包括:如何通过固有选择性ALD实现接近完美的选择性(99.999999%)以及如何精确控制初始形核阶段形核连续和提高薄膜质量。当薄膜达到一定厚度后发生非生长区域形核,降低堆叠结构的自对准沉积精度,因此调控选择性沉积过程中非生长区域的缺陷迁移去除也是一个重要的研究课题。

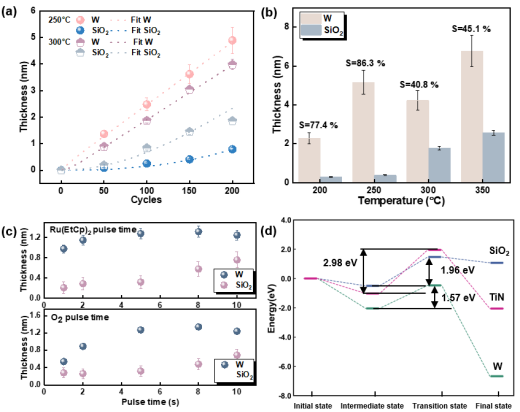

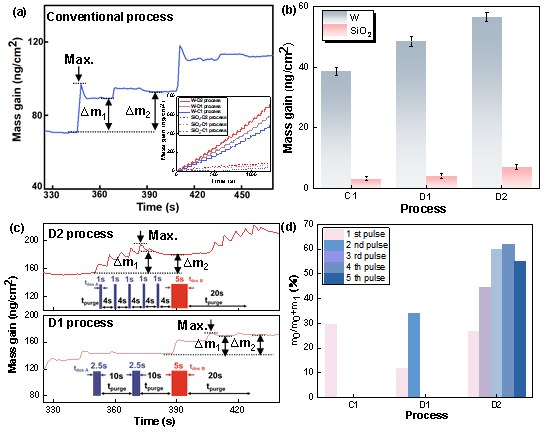

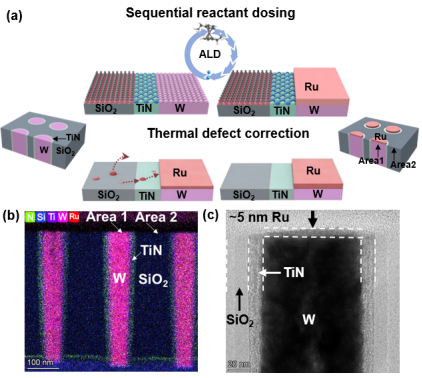

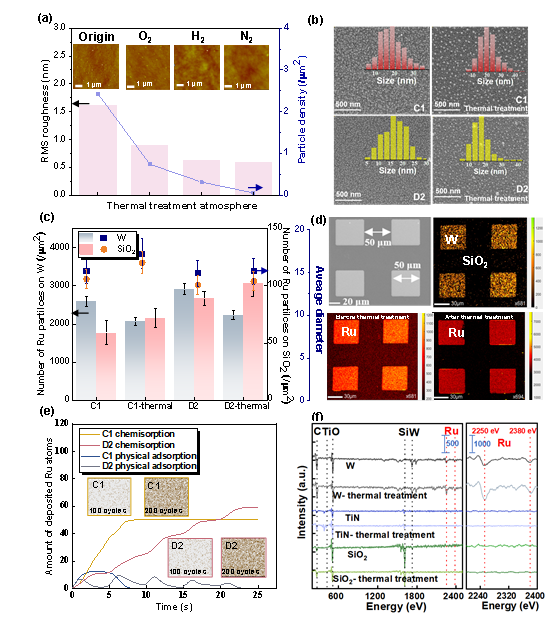

近期,华中科技大学微纳中心陈蓉教授团队提出了一种“化繁为简”的高精度薄膜沉积解决方案,他们采用多次短脉冲工艺耦合缺陷热处理的固有选择性原子层沉积(ALD)工艺,在金属-氧化物的图案衬底进行了金属堆叠沉积的研究。金属Ru在金属W表现出选择性沉积,在SiO2/TiN没有可观察到的生长。获得了100%的最佳选择性,并且沉积在W上的膜的最大厚度达到5nm。相比于繁琐的光刻、刻蚀等多步工序,上述选择性原子层沉积可以实现在金属互连机构中衬底上“一步法”金属选择性对准生长。通过该方法可提升集成电路制造效率与精准度、降低金属互联电阻率、有望加速半导体领域小型化工艺的进展,为下一代纳米制造工艺提供新的方向。

文章总览:

原子尺度的高精度对准是下一代纳米电子学制造的瓶颈。在这项研究中,引入了多次短脉冲耦合缺陷迁移后处理的固有选择性原子层沉积(ALD)来应对这一挑战。通过优化脉冲工艺,进行多次分布脉冲ALD工艺,有效控制初始金属形核粒径,密度,提高薄膜致密度,降低最小成膜厚度以及降低约15%电阻率。此外,通过退火缺陷迁移理论对样品进行后处理使得非生长区域缺陷迁移至生长区,在不引入杂质的前提下实现提高选择性;最终金属Ru薄膜被成功地沉积在W/TiN/SiO2纳米图案上,避免了边缘处的“蘑菇”状过度生长以及在SiO2和TiN表面出现不期望的成核缺陷。在金属W上的膜厚大约5 nm,选择性几乎达到100%。这种方法提供了一种可集成和高精度的自对准制造技术,这有利于未来集成电路金属互联的继续微缩。

图文解析:

总结展望:

通过退火缺陷迁移理论对样品进行后处理使得非生长区域缺陷迁移至生长区,在不引入杂质的前提下实现提高选择性;最终金属Ru薄膜被成功地沉积在W/TiN/SiO2纳米图案上,避免了边缘处的“蘑菇”状过度生长以及在SiO2和TiN表面出现不期望的成核缺陷。在金属W上的膜厚大约5 nm,选择性几乎达到100%。对于金属互连这一结构,后续可以继续通过脉冲工艺优化耦合嵌套热处理缺陷超循环实现更厚,更致密以及电阻率更低的金属互连结构,这样也满足集成电路领域小型化发展的市场需求。